Нет товаров

Товар добавлен в корзину

Товаров в корзине: 0. Сейчас в корзине 1 товар.

N4877A

N4877A

N4877A Clock Data Recovery & Demultiplexer

- Убрать этот товар из моего избранного.

- Добавить этот товар в избранное.

- Печать

Описание - N4877A

Загрузить техническое описание

Characterize Next-generation Receivers and Transmitters

The N4877A Clock Data Recovery is designed to operate over from 50 Mb/s to 32 Gb/s. The wide data rate range allows testing of emerging standards like 100GbE and 32GFC while covering existing lower speed standards. The 16G option operating up to 16.5 Gb/s is ideal for 16GFC as well as computer standards like USB 3.0, SATA, SAS and PCIe including PCIe gen4.

Recover Clocks or Clean-Up Clocks

The N4877A provides necessary clock signals for BERTs or oscilloscopes when access to appropriate clock signals from the device under test (DUT) is not possible. The N4877A recovers clocks from data streams if a clock is not available or can act as clean-up PLL for existing clocks with excessive intrinsic jitter to allow accurate measurements.

Simplify Receiver Testing of high speed Devices

The N4877A Clock Data Recovery and Demultiplexer 1:2 is the counterpart to the N4876A Multiplexer 2:1 and complements Keysight's J-BERT and ParBERT based receiver test solutions for data rates between 12.5 Gb/s and 28.4 Gb/s.

SW controlled swappable demultiplexer outputs, a Jitter Tolerance Test mode and connection cable kits specially designed for J-BERT N4903B simplify receiver testing.

Measure the real Performance of clock less Devices

Low intrinsic jitter paired with tunable loop bandwidth, selectable peaking and high sensitivity enable accurate measurements of transmitters.

The N4877A’s auxiliary clock output provides ultralow intrinsic random jitter of less than a 100 fs rms making it the ideal companion for sampling scopes equipped with a precision timebase.

Easily Control all Settings

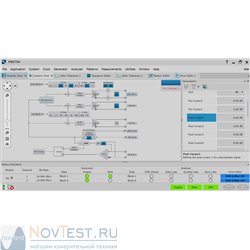

The settings of the N4877A Clock Data Recovery and Demultiplexer can be controlled through its rear-panel USB connection and a standalone user interface that runs on a Windows® PC. The SW can be installed on instruments running Windows® XP or Windows® 7

PLL and Jitter Spectrum Analysis

Use 86100CU-400 or 86100DU-400 software to make fast, accurate and repeatable measurements of phase-locked loop (PLL) bandwidth/jitter transfer. With a precision jitter source a clock data recovery (N4877A, 83496B or N1070A) can be configured as a jitter receiver to create a PLL stimulus-response test system.

- Operates from 50 Mb/s to 32 Gb/s providing important headroom for forward error correction and proprietary rates

- Tunable loop bandwidth up to 20 MHz and selectable peaking for to meet industry standards

- Clock and auxiliary clock output with residual jitter as low as 100 fs rms for precision waveform analysis with the 86100 Digital Communications Analyzer

- Built-in demultiplexer generates subrate data streams for economical BER testing

- Sensitive data input for small signals

- Easy to use graphical user interface via USB connection to a PC