No products

Product successfully added to your shopping cart

There are 0 items in your cart. There is 1 item in your cart.

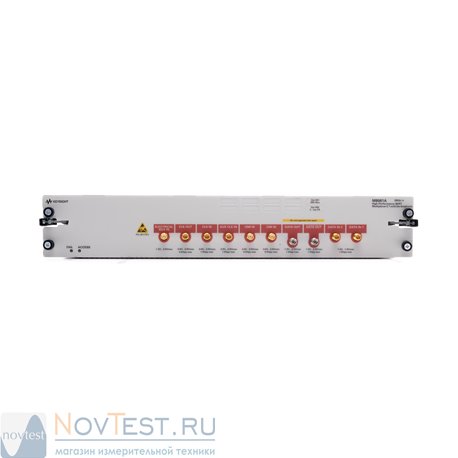

M8061A

M8061A

M8061A Multiplexer 2:1 With De-Emphasis 32 Gb/s

- Remove this product from my favorite's list.

- Add this product to my list of favorites.

More info - M8061A

Загрузить техническое описание

R&D and test engineers who need to characterize serial interfaces of up to 28.4 Gb/s can use the M8061A 2:1 Multiplexer with optional de-emphasis to extend the rate of J-BERT N4903B pattern generator. For the most accurate receiver characterization results, the M8061A provides four calibrated de-emphasis taps, which can be extended to eight taps, built-in superposition of level interference and Clock/2 jitter injection. The M8061A is a 2-slot AXIe module that can be controlled via USB from J-BERT’s user interface.

Application examples for M8061A:

- Optical transceivers such as 100GBASE-LR4, -SR4 and -ER4, 32G Fibre Channel

- SERDES and chip-to-chip interfaces, such as OIF CEI

- Backplanes, cables, such as 100GBASE-KR4, -CR4

- Next generation computer buses, such as PCI Express ® 4

Emulate transmitter de-emphasis with up to 8 taps

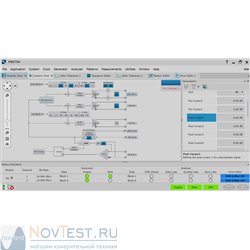

Many multi gigabit serial interfaces use transmitter de-emphasis to compensate for electrical signal degradations caused by printed circuit boards or cables between the transmitter and the receiver ports. R&D and test engineers who need to characterize receiver ports under realistic and worst case conditions require a pattern generator that allows to accurately emulate transmitter de-emphasis with adjustable multi-tap de-emphasis levels. The M8061A can be used in combination with J-BERT N4903B as shown below.

This setup shows how to emulate transmitter de-emphasis up to 28.4 Gb/s with M8061A and J-BERT N4903B. (4 tap de-emphasis with 1 pre and two post-cursors is shown)

De-embed signal degradations caused by the test set up and fixtures using de-emphasis

Minimizing the influence of the test environment is a challenge especially if bit rates exceed 20 Gb/s. To de-embed the signal degradations caused by cables, test fixtures, adapters, etc, the de-emphasis technique is commonly used. M8061A is the only instrument that offers up to 8 tap de-emphasis up to 28.4 Gb/s, allowing compensation of signal degradations in very fine steps.

PCI Express is a registered trademark of PCI-SIG

- Expands data rate of J-BERT N4903B pattern generator up to 28.4 Gb/s

- Adjustable positive and negative de-emphasis for up to 8 taps, optional

- Internal superposition of interference for common-mode and differential mode

- Transparent to jitter generated by J-BERT

- Clock/2 jitter can be added

- Electrical idle

- Control from J-BERT N4903B user interface via USB