Корзина 0 товар товара(ов) (пусто)

Нет товаров

Бесплатная доставка! Доставка:

$0 Итого, к оплате:

Товар добавлен в корзину

Количество

Итого, к оплате:

Товаров в корзине: 0. Сейчас в корзине 1 товар.

Стоимость: (вкл. НДС)

Стоимость доставки (вкл. НДС) Бесплатная доставка!

Итого, к оплате: (вкл. НДС)

Увеличить

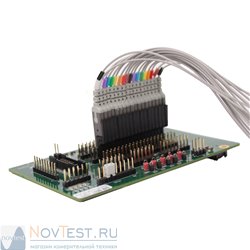

Увеличить E8140A

E8140A

E8140A LVDS Pattern Generator Clock Pod

- Убрать этот товар из моего избранного.

- Добавить этот товар в избранное.

- Печать

Описание - E8140A

Загрузить техническое описание

The LVDS clock pod supports Keysight Technologies 16720A and 1670G-004 pattern generators. Each pattern generator requires at least one clock pod, up to 4 data pods, and lead sets for each clock and data pod. For each E8142A clock pod that you will be using, you will need one (1) 10498A lead set.

- Clock output type: 65LVDS179 (LVDS) and 10H125 (TTL)

- Clock output rate: 200 MHz maximum (LVDS and TTL)

- Clock out delay: ~8ns in 14 steps

- Clock input type: 65LVDS179 (LVDS with 100 ohm)

- Clock input rate: DC to 150 MHz (LVDS)

- Pattern input rate: 10H124 (TTL) ( no connect = logic 1)

- Clock in to clock out: approximately 30 ns

- Pattern in to recognition: approximately 15 ns + 1 clock period

- Recommended lead set: 10498A

Clock Pod Configuration

- Logic level support: ?LVDS

- Recommended lead set: Keysight 10498A

- Order at least one clock pod for each pattern generator module used as a master or each 1682xA portable logic analyzer

- Design in a dedicated header for pod connection or order one 8-channel lead set for each pod

Clock Output

- Clock output type: 65LVDS179 (LVDS) and 10H125 (TTL)

- Clock output rate: 200 MHz maximum (LVDS and TTL)

- Clock out delay: ~8 ns total in 14 steps

Clock Input

- Clock input type: 65LVDS179 (LVDS with 100 ohm)

- Clock input rate: DC to 150 MHz (LVDS)

- Clock in to clock out: approximately 30 ns

Pattern Input

- Pattern input rate: 10H124 (TTL) ( no connect = logic 1)

- Pattern in to recognition: approximately 15 ns + 1 clock period