Cart 0 Product Products (empty)

No products

Free shipping! Shipping

$0 Total

Product successfully added to your shopping cart

Quantity

Total

There are 0 items in your cart. There is 1 item in your cart.

Total products (tax incl.)

Total shipping (tax incl.) Free shipping!

Total (tax incl.)

View larger

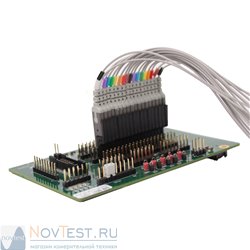

View larger E8140A

E8140A

E8140A LVDS Pattern Generator Clock Pod

- Remove this product from my favorite's list.

- Add this product to my list of favorites.

More info - E8140A

Загрузить техническое описание

The LVDS clock pod supports Keysight Technologies 16720A and 1670G-004 pattern generators. Each pattern generator requires at least one clock pod, up to 4 data pods, and lead sets for each clock and data pod. For each E8142A clock pod that you will be using, you will need one (1) 10498A lead set.

- Clock output type: 65LVDS179 (LVDS) and 10H125 (TTL)

- Clock output rate: 200 MHz maximum (LVDS and TTL)

- Clock out delay: ~8ns in 14 steps

- Clock input type: 65LVDS179 (LVDS with 100 ohm)

- Clock input rate: DC to 150 MHz (LVDS)

- Pattern input rate: 10H124 (TTL) ( no connect = logic 1)

- Clock in to clock out: approximately 30 ns

- Pattern in to recognition: approximately 15 ns + 1 clock period

- Recommended lead set: 10498A

Clock Pod Configuration

- Logic level support: ?LVDS

- Recommended lead set: Keysight 10498A

- Order at least one clock pod for each pattern generator module used as a master or each 1682xA portable logic analyzer

- Design in a dedicated header for pod connection or order one 8-channel lead set for each pod

Clock Output

- Clock output type: 65LVDS179 (LVDS) and 10H125 (TTL)

- Clock output rate: 200 MHz maximum (LVDS and TTL)

- Clock out delay: ~8 ns total in 14 steps

Clock Input

- Clock input type: 65LVDS179 (LVDS with 100 ohm)

- Clock input rate: DC to 150 MHz (LVDS)

- Clock in to clock out: approximately 30 ns

Pattern Input

- Pattern input rate: 10H124 (TTL) ( no connect = logic 1)

- Pattern in to recognition: approximately 15 ns + 1 clock period